### e-ISSN: 2395 - 7639

## INTERNATIONAL JOURNAL OF MULTIDISCIPLINARY RESEARCH

IN SCIENCE, ENGINEERING, TECHNOLOGY AND MANAGEMENT

Volume 9, Issue 7, July 2022

@

INTERNATIONAL STANDARD SERIAL NUMBER INDIA

Impact Factor: 7.580

ili in the second secon

| ISSN: 2395-7639 | <u>www.ijmrsetm.com</u> | Impact Factor: 7.580|

Volume 9, Issue 7, July 2022

DOI: 10.15680/LJMRSETM.2022.0907010

## Research on Analysis of Average Power Consumption & Propagation delay of Various Digital Adders

#### Mr.Prabhat Pandey, Mrs. Kirandeep

M.Tech, Department of Electronics and Communication Engineering, S K I T M, Bahadurgarh, Haryana, India

Assistant Professor, Department of Electronics and Communication Engineering, S K I T M, Bahadurgarh

Haryana, India

**ABSTRACT:** Adders are the core part of advanced arithmetic operations like addition, multiplication ,division ,mathematical process etc. In most of those systems adder lies with in the essential path that affects the speed of the system. To satisfy these demands, power consumption and propagation delay should be reduced in adder cell that is that the basic building block. Adders are one in every of the foremost wide used digital elements within the digital micro circuit style and area unit the required a part of Digital Signal process (DSP) applications. With the advances in technology, researchers have tried and are attempting to style adders which provide either high speed, low power consumption, less pace or the mixture of them. During this project, numerous digital adders equivalent toHalf MOS Adder, FullAdder, Ripple Carry Adder(RCA), are a unit designed using MOSFET in 32nm Technology length. They're simulated employing HSPICE and also the performance parameters of adder's equivalent to average power and delay are determined. A twin mode low power technique is applied on Ripple Carry Adder to cut backpower

#### I. INTRODUCTION

Extremely Scaled Integration or VLSI may be a system which recommends to make incorporated circuits by joining a many transistor-based circuits into one chip. The chip may be a VLSI gadget. Every last chip industrial facility influenced nowadays to utilize VLSI designs. Current innovation has jumped from the occasion of bigger transistors on a chip to a chip with un numerable entryways and billions of individual transistors of small size. as a result of this changed set up it discovers scope at interims the fields of superior registering and correspondence frameworks, unbiased systems, wafer-scale incorporation, regular rationality frameworks and investigation and improvement. So there is a rising interest for these chip driven stock at interims the blessing and prospective future. To full fill with these requests we've a slant to should decrease the size, power, and intensity. Out of that power dissemination has turned into a critical target at interims the outline of each simple and computerized circuit. It's incontestable that attributable to ignoring short out present, past systems intended to upgrade the domain of a fan-out tree may prompt inordinate power utilization. the general dynamic mode control utilization, the clock power, thus the basic outpouring energy of the combinatory circuits are diminished by up to fifty fifth , 29%, and 53%, severally, though keeping up comparative speed and information solidness when contrasted with the circuits upheld in CMOS innovation.

#### Motivation:

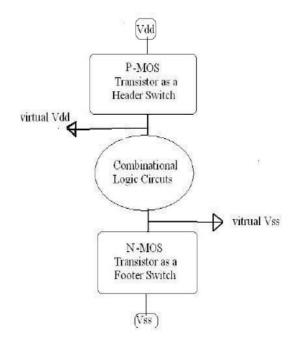

With innovation scaling, spill age current and ground ricochetis exponentially expanding. Power gating is generally actualized to stifle the spillage power and ground commotion instand by mode. Moreover, amid the mode changes, particularly from rest mode to dynamic mode, the power gating plans cause ground ricochet that enormously influences the unwavering quality of circuits. This persuadesmeto outline some new structures to decrease the power.

#### **II. LITERATURE REVIEW**

Literature Survey Several circuit techniques have been developed to reduce delays and power consumption in a standard adder load cycle. In this section, I will introduce a summary of some of the key strategies used to reduce delays, as well as energy consumption.

| ISSN: 2395-7639 | <u>www.ijmrsetm.com</u> | Impact Factor: 7.580|

Volume 9, Issue 7, July 2022

#### | DOI: 10.15680/LJMRSETM.2022.0907010 |

2.1 SEMICONDUCTOR DEVICE MODELS Silicon plays an important role in the semiconductor business and many semiconductor gadget models rely on silicon materials. This section provides a brief introduction to conventional semiconductor gadgets and the development of these gadgets over the past decades. A semiconductor is a type of solid object in which the electrical conductor is between a channel and a separator. Its unique transport features are controlled by small belt holes, which allow various environmental variables including temperature and light to control its electrical properties

[1]. A p-n intersection is a structure formed by combining p-sort semiconductors and n-type together in close proximity [2]. The term merging refers to the area where two semiconductors meet. The p-n intersection is often connected as the basic structure in modern hardware. Outstanding among the well-known elements at intersections p-n is the diode. In the p-n diode, the available energy can flow from the p (anode) side to the n (cathode) type, but it cannot transmit otherwise. Outstanding among the most important semiconductor gadgets is the bipolar intersection transistor (BJT), which was built at Bell Laboratories in 1947. In BJTs, two electrons and gaps take an interest in the conduction process. Bipolar transistors are widely used as part of high-speed circuits, light circuits, and power consumption. Field-impact transistor (FET) is a type of power-based transistor that controls the flow of a single type of charging vehicle to a semiconductor device. Existing FETs are called unipolar transistors to separate single-person transport operations and double transporter transcripts for BJTs

[3]. A common metal-oxide-semiconductor (MOS) structure is obtained by keeping a layer of silicon dioxide (SiO2) and a metal layer over the semiconductor kick bucket. As silicon dioxide is a dielectric material its structure is equivalent to a planar capacitor, with one anode being replaced by a semiconductor

[3]. MOSFET (metal-oxide-semiconductor field-impact transistor) was developed by Kahng and Atalla in 1960. In MOSFET, the source and deplete are connected to an overhead direction where the carriers can flow when they are officially adjusted by the voltage of the door. The source and the reduced areas can be p or n, however both should be the same type, and be the opposite type of body. Since then, MOSFETs have been completely reduced and the Si-SiO2 optical connector remains the most important component two or more digital binary numbers. In many forums and different types / types of processing, add-ons are often used in large quantities including rational counting of logical units, as well as in various processor components, where they are used to obtain addresses. , table lists, and comparable functions. Adder is a composite logic circuit used to generate total and load inputs. As we know in the combined logic circuit different inputs are used by a certain concept to produce output. Examples of logical circuit logic are adder, multiplexer, decoder etc. Half Adder: A half adder is a basic, customizable computer circuit used for two logical pieces as shown in Figure 2.1.

IJMRSETM

| ISSN: 2395-7639 | www.ijmrsetm.com | Impact Factor: 7.580|

Volume 9, Issue 7, July 2022

#### DOI: 10.15680/IJMRSETM.2022.0907010

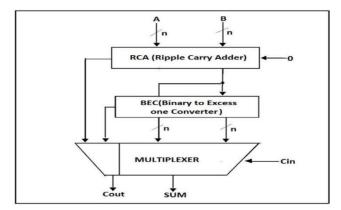

#### **CONVENTIONAL BEC Based CSLA:**

B. Ramkumar and H. M. Kittur praised the lower power & local capacity CSIA made with one RCA and one BEC (Binary to Excess One Converter) than a double RCA. The structure of the selected adder appears in Figure

Harmful development used by various gadgets in everyday life at the end of the breed

superior Very Large Scale Integration (VLSI) frameworks. Different analysts are declining far from developing VLSI frameworks to region, control, delays and more. The repetition is critical square is a juggling unit of numbers. Rapid and regional duplication is required various Digital Signal Processing (DSP) statistics. The enhanced Ved expansion is used as a part of various DSP programs such as convolution, Fast Fourier Transform and chip applications. Advanced Ved science is an old system of numbers. Advanced Ved name obtained from "Veda" and its significance "storage space". By using sutras Advanced Ved arithmetic actually reduces the type of arithmetic. It requires less calculation time and less resources to use. These sutras are basically used with a decimal increase of two numbers; and here it is extended to double its size.

Types of Blending For gadgets, adder or summer computer circuit that extends numbers. On most PCs and different types of processors, add-ons are used in rational juggling units, as well as in different parts of the processor, where they are used to find addresses, table records, and similar functions. Apart from the fact that additions can be enhanced by the display of numbers, for example, decimal decimals or multiplication of 3, the most common additions apply to corresponding numbers and appendix 2 or appendix 1 are used to denote a negative number.

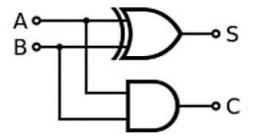

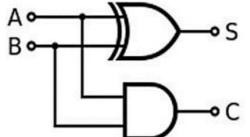

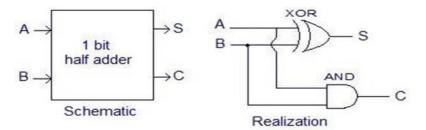

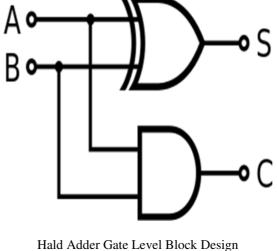

**3.1 Half Adder**: A half adder is a straightforward, practical computer circuit made up of two sensible doors. The half adder adds to the double-digit number (AB). The yield is the sum of two pieces (S) and bearing (C).

Figure 3.1: Schematic diagram of Half Adder Table 3.1: Truth Table of Half Adder

IJMRSETM

| ISSN: 2395-7639 | <u>www.ijmrsetm.com</u> | Impact Factor: 7.580|

Volume 9, Issue 7, July 2022

| Input |   | Output |       |

|-------|---|--------|-------|

| Α     | В | Sum    | Carry |

| 0     | 0 | 0      | 0     |

| 0     | 1 | 1      | 0     |

| 1     | 0 | 1      | 0     |

| 1     | 1 | 0      | 1     |

#### | DOI: 10.15680/LJMRSETM.2022.0907010 |

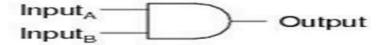

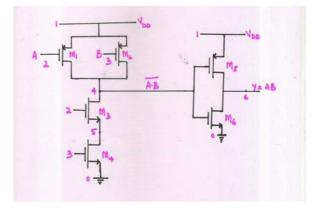

#### **Implementation AND GATE:**

Function ONLY mentioned by AB or A.B. 2 Knowledge output AND door is high if both sources are high. The picture and reality table AND entryway appears in Figure 4.1 and Table 4.1 individually.

| А | в | Output |  |

|---|---|--------|--|

| 0 | 0 | 0      |  |

| 0 | 1 | 0      |  |

| 1 | 0 | 0      |  |

| 1 | 1 | 1      |  |

The AND Gate is realized using MOSFETS as shown in figure

The simulated output of AND gate is shown in figure

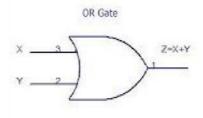

#### **Implementation OR GATE**

Use of the gate OR: Or on the other hand a consistent work that gives yield 1 if the information not less than one is respectful 1, and usually gives a rating of 0. Function OR integrated by A + B. The picture table and the reality of the OR door appear in the image It is clear from the waveforms obtained after mimicking that the OR door yield is high if the data source is high and low if both data sources are low, later full. completes the fact sheet OR the entry method as appears in Table 4.2. 4.3 I

ISSN: 2395-7639 | www.ijmrsetm.com | Impact Factor: 7.580

Volume 9, Issue 7, July 2022

#### | DOI: 10.15680/LJMRSETM.2022.0907010 |

Figure 4.5: Realization of OR gate using MOSFETs

| INF | *UTS | OUTPUT |

|-----|------|--------|

| x   | Y    | z      |

| 0   | 0    | 0      |

| 0   | 1    | 1      |

| 1   | 0    | 1      |

| 1   | 1    | 1      |

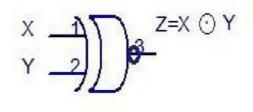

**XNOR gateway implementation**: The XNOR department (here and there translated by its extended name, Exclusive NOR entryway) is an advanced login with at least two sources and one crop that makes sense. XNOR login yield is high when most of its sources are high or when most of its data sources are low. The picture and reality table for XNOR entryway appear in Figure 4.20 and Table 4.7 respectively and the mind circuit appears in Figure 4.21.

Figure 4.20: Logic Symbol of XNOR gate Table

| Table 4. | .7: Trutl | n Table | of XNOR | gate |

|----------|-----------|---------|---------|------|

|          |           |         |         |      |

| INF | PUTS | OUTPUT |

|-----|------|--------|

| x   | Y    | z      |

| 0   | 0    | 1      |

| 0   | 1    | 0      |

| 1   | 0    | 0      |

| 1   | 1    | 1      |

ijmrsetm

| ISSN: 2395-7639 | <u>www.ijmrsetm.com</u> | Impact Factor: 7.580|

Volume 9, Issue 7, July 2022

#### | DOI: 10.15680/IJMRSETM.2022.0907010 |

🔐 🧿 💸 IJMRSETM

| ISSN: 2395-7639 | www.ijmrsetm.com | Impact Factor: 7.580

Volume 9, Issue 7, July 2022

#

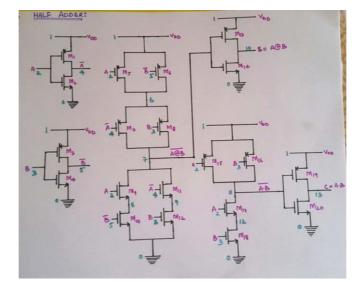

**Use of Half Adder:** A half adder is a combination of numbers that combines two numbers and creates a whole piece (S) and a carry bit (C) as a crop. In the case where An and B are pieces of information, at that point the total value (S) is X X by Ani and B and carry bit (C) will be AND A's and B's. From this no doubt a half adder circuit can be easily upgraded using one X-OR and one-door AND ENTRY door. Half adder is the easiest adder circuit, but it has significant drawbacks. The half adder can include only two pieces of information (An and B) and has nothing to do with carrying if any information. So if the contribution to the half adder has a load, then it will be dismissed and includes only An and B pieces. That means that the same expansion process is not yet complete and that is why it is known as the half adder. The scheme framework, mind region and the true half adder table appear in Figure 4.24 and Table 4.8 individually.

Truth Table of Half Adder

| Inp | outs | Out | puts |

|-----|------|-----|------|

| A   | в    | S   | С    |

| 0   | 0    | 0   | 0    |

| 1   | 0    | 1   | 0    |

| 0   | 1    | 1   | 0    |

| 1   | 1    | 0   | 1    |

ijmrsetm

| ISSN: 2395-7639 | <u>www.ijmrsetm.com</u> | Impact Factor: 7.580|

Volume 9, Issue 7, July 2022

#### | DOI: 10.15680/IJMRSETM.2022.0907010 |

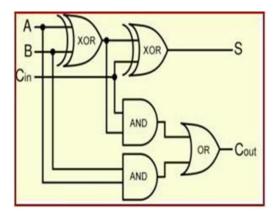

**Use of Full Adder**: A full adder is a unit that combines two numbers and a bearing, and creates a complete and carrying. The full adder cycle includes three single-digit numbers (A, B, Cin) and displays two single-digit numbers (S, Cout). A sensible circuit for the full adder is shown in Figure 4.27 and the actual table appears in Table 4.9.

International Journal of Multidisciplinary Research in Science, Engineering, Technology & Management (IJMRSETM)

| ISSN: 2395-7639 | www.ijmrsetm.com | Impact Factor: 7.580|

Volume 9, Issue 7, July 2022

#### | DOI: 10.15680/IJMRSETM.2022.0907010 |

#### **III. CONCLUSION**

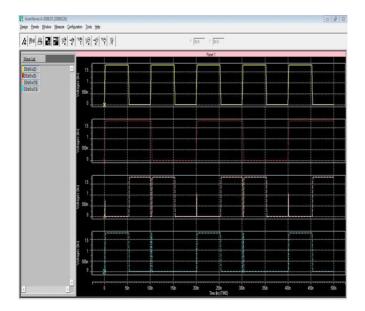

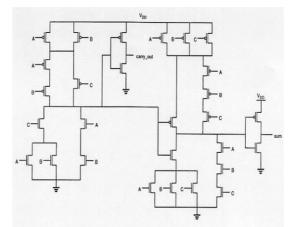

Subsequent redesign is verified in HSPICE shortcuts using circuit frame hub hoods, regional chart harbors are provided with a unique hub phone, where MosFET variants from BSIM are covered and mimicked. (Figure 5.1) Figure 5.1:

Full Adder Design Block Diagram for Transistor Level

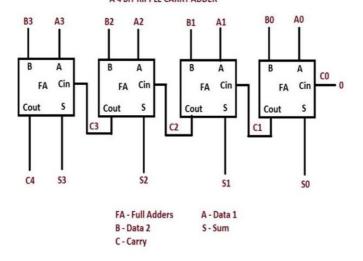

Hald Adder Gate Level Block Design Ripple carry Adder A 4 BIT RIPPLE CARRY ADDER

| ISSN: 2395-7639 | www.ijmrsetm.com | Impact Factor: 7.580

Volume 9, Issue 7, July 2022

#### DOI: 10.15680/IJMRSETM.2022.0907010

Ripple carry Adder

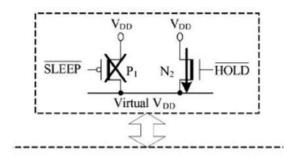

Figure 5.4: Dual Mode Technique Basic Block Diagram

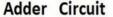

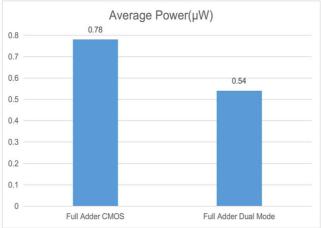

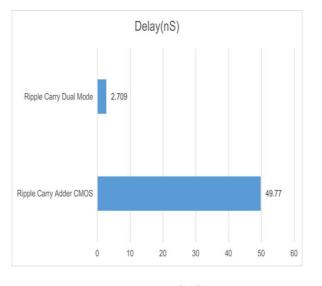

Complete Drawing of AdderDesign Block of Transistor Level Figure 5.2 and 5.3 represent a half-adder and ripple carry adder design and Figure 5.4 shows representation of dual mode. Figure 5.4: Dual Mode Technique Basic Block Diagram Two modes are involved in dual mode mode, one for capture mode and the other for sleep mode. Medium strength and delays are listed and summarized below: Results are available for HSPICE software synopsy and MosFET models on the PTM website, namely the Predictive Technology Model. Adder is applied to Mosnet 32nm Technology using the standard CMOS method and dual mode mode. The results show that the dual mode method works best in terms of power consumption and latency. In Figure 5.5, the power comparison chart ratio is shown in the full adder, similar to Figure 5.6, for the half adder. For ripple carry adder Figures 5.7 and 5.8 show medium power charts and delays.

| ISSN: 2395-7639 | <u>www.ijmrsetm.com</u> | Impact Factor: 7.580

Volume 9, Issue 7, July 2022

#### DOI: 10.15680/IJMRSETM.2022.0907010

Average Power Full Adder

Therefor Figure 5.6: Average Power Half Adder

#### REFERENCES

P. Balasubramanian, "Rated Ripple transmits additives and conveys forward similar statistics" IEEE, October 2017

Sarabdeep Singh, Dilip Kumar, Design of Area and Power Efficient Modified Carry Select Adder, International Journal of Computer Applications, vol.33, no.3, pp.14-18, Nov2011.

[3] www.circuitstoday.com/swell pass on adder

[4] Look forward to adder Hardware rating for math modules, ARITH investigates collection, Aoki lab, Tohoku University

[5] International Journal of Advanced Research in Computer Engineering and Communication Vol. 3, Issue 10, October 2014 Copyright to IJARCCE www.ijarcce.com 8341 Use of Ripple Carry and Carry Skip Adders With Speed and Area Efficient PUSHPALATHA CHOPPA, B.N. SRINIVASA RAO

[6] www.barrywatson.se/dd/dd\_Carry \_select\_adder.html [8] tams-www.informatik.uni-hamburg. de / applets / hades / webdemos / 20-numberjuggling / 65-csa- mult / csa6.html

[9] ArkadiyMorgenshtein, Alexander Fish and Israel A.Wagner "Entryway Diffusion Input (GDI): Energy Efficient Integrated Digital Circuits", IEEE alternates in VLSI Systems, vol.10, and .5, pages 566-581, October 2002.

[10] Moradi, F. Wisland, D.T. Mahmoodi, H. Aunet, Tuan Vu Cao and Peiravi "Ultra low power full adder topologies", in: Proceedings of the IEEE International Symposium on Circuits and Systems, ISCAS, pp. 3158, 3161, May 2009.

International Journal of Multidisciplinary Research in Science, Engineering, Technology & Management (IJMRSETM)

ijmrsetm

| ISSN: 2395-7639 | <u>www.ijmrsetm.com</u> | Impact Factor: 7.580|

Volume 9, Issue 7, July 2022

| DOI: 10.15680/IJMRSETM.2022.0907010 |

[11] Po-Ming Lee, Chia-Hao Hsu and Yun-Hsiun Hung, "Complete Novel 10-T Approved Approved by GDI Building ", in: Procedures for IEEE International Symposium on Integrated Circuits (ISIC), pp.115,118, September 2007.

[12] Q. Wu, P. Massoud, X.Yu, "Clock-Gating and Its Performance in Low-Income Circular Power Design," in Proceedings of the IEEE Conference on Custom Integrated Circuits, pp. 425-435, September 1997.

[13] PadmanabhanBalasubramanian and John John "The Low Power Digital outline implements a modified GDI

strategy", entitled: Procedures for International Conference on Design and Testing Integrated Systems in Nanoscale Technology, DTIS, pp.190,193, Sept. 2006.

[14] Dubey, V. Sairam, R., "An Arithmetic and Logic Unit Optimized for Area and Power", in: Proceedings of the International Conference on Advanced Computing and Communication Technologies (ACCT), pp.330, 334, Feb. 2014.

[15] Manjunatha Reddy, B.N. Sheshagiri, H.N. Vijayakumar and B.R. Shanthala, "Making Low-Power 8-Bit Multiplier Using Gate Diffusion Input Logic", entitled: Proceedings of the 17th IEEE International Conference on Computational Science and Engineering (CSE), pp.1868, 1871, Dec. 2014.

[16] AlirezaSaberkari and ShahriarBaradaranShokouhi, "Novel low-control CMOS 1-bit add-on full GDI method", at: IJME-INTERTECH Conference Procedures, pages 758,765, August 2006

# **INTERNATIONAL JOURNAL** OF MULTIDISCIPLINARY RESEARCH

IN SCIENCE, ENGINEERING, TECHNOLOGY AND MANAGEMENT

+91 99405 72462

🕥 +91 63819 07438 🔀 ijmrsetm@gmail.com

www.ijmrsetm.com